LTOL low temperature entanglement with thermal carriers

LTOL test, full English name is Low temperature operating Life, abbreviated as LTOL. Its main test is generally based on JESD22-A108, the specific test conditions are: junction temperature (Tj)≦50 °C, voltage Vcc≧Vccmax, test time: 1000hrs number of samples: 32 per batch; Test duration: 1000 hours. In general, the actual low temperature test is generally much lower than this temperature, such as -55 ~ 0 °C low temperature range test and so on. The purpose of the LTOL test is mainly for the degradation of hot carriers, because the injection effect of hot carriers will be more obvious at low temperatures, so this scheme is used to judge.

Test Attach:

Different chip types will have different test methods for this test, such as flash chips, which need to ensure the normal high-speed reading and writing status of the chip while testing, so as to determine the reliability of the chip; Another example is the car gauge chip, its test conditions will be more demanding, the low temperature test we mentioned earlier, the general -55 °C test is the norm.

However, LTOL's test standards are not only JEDEC standards, there are other standards, this follow-up user actual test design to confirm, at present, the minimum limit is -80 °C, but the actual test of the chip is generally at -55 °C, this also needs to be based on the actual requirements of the user, some special chips, may have special low temperature test requirements.

The corresponding test needs to correspond to the corresponding test material:

At present, the mainstream chip aging test, high and low temperature test are the use of chip aging test holder, to the above test requirements, EEPROM SOIC8 package chip LTOL test as an example, Ta temperature range -55 ~ 50 °C, the voltage needs to be greater than its rated voltage 1.8 ~ 5.5V wide voltage device maximum, the number of single board test samples can be designed according to the standard 32EA/group, while designing the number of SOIC8 aging seats on the aging board according to the space of the aging furnace, This allows more chips to be tested in limited space, thereby improving the test efficiency of LTOL. All the devices on the aging test seat and the aging board such as the PCB board need to meet or exceed the requirements of its test to complete the LTOL test well, otherwise it is easy to play the situation that the equipment is not successful first, which is time-consuming and expensive, and more troublesome is to delay the test progress of the entire project. At present, the domestic aging seat and the increasingly mature, especially the SOIC, SOP, QFN, QFP and other general packaging forms of aging seat, has long completed the process of mass production mold standardization, aging test seat can be easily purchased in a treasure or these enterprise network sites. Companies known to have these LTOL-compliant aging test seats include, but are not limited to, Shenzhen Hongyi Electronics Co., Ltd., Shenzhen Kaizhitong Microelectronics Co., Ltd., Shanyi Electromechanical domestic agents, Sensata China Branch, etc.

In terms of semiconductor test consumables, domestic is becoming more and more mature, and in some areas has fully replaced Japanese and Korean products, so when choosing and designing their own company's aging test, we must pay attention to confirm the good direction and set the position, so as to choose all the materials that are more suitable for the LTOL test of their own company's products.

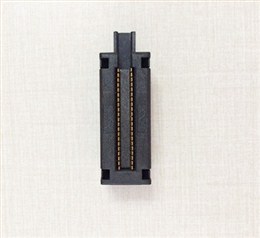

TQFP100 FQFP100 QFP100 burn in socket

TQFP100 FQFP100 QFP100 burn in socket High frequency socket-2.5GHz test socket

High frequency socket-2.5GHz test socket SMT/SMD capacitor burn in test socket

SMT/SMD capacitor burn in test socket TSOP48 burn in socket

TSOP48 burn in socket